SFQ-based on-chip digital readout for HPC-QC integration

HPCQC @CINECA, Italy – Dec 14<sup>th</sup>, 2023 Marco Arzeo, Lab manager at SEEQC-EU

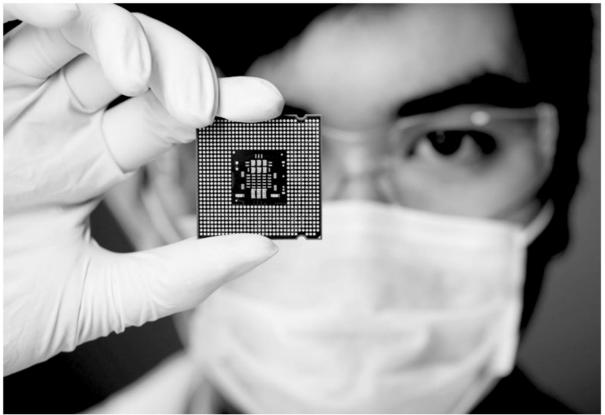

#### State-of-the-art CMOS chip

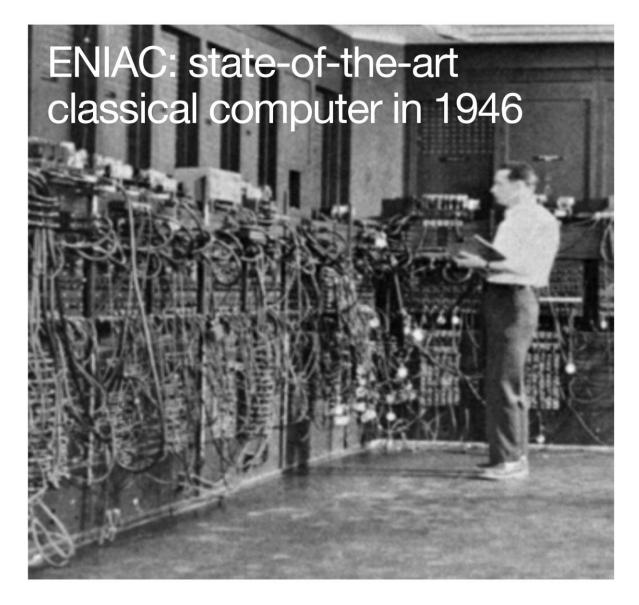

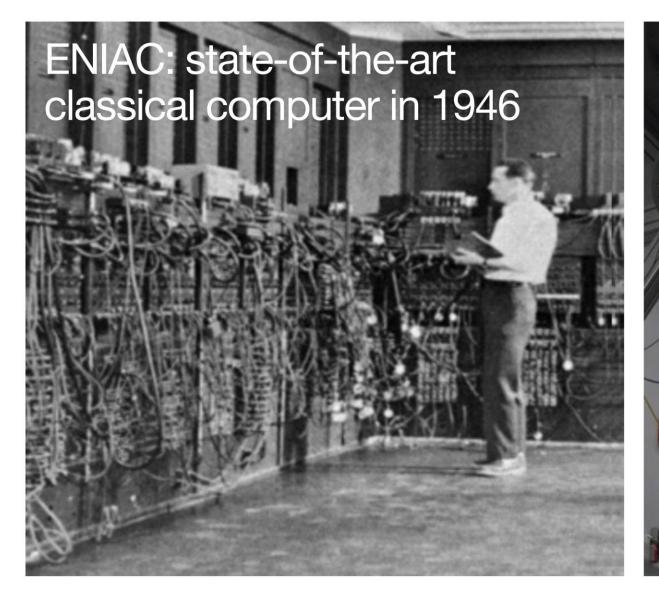

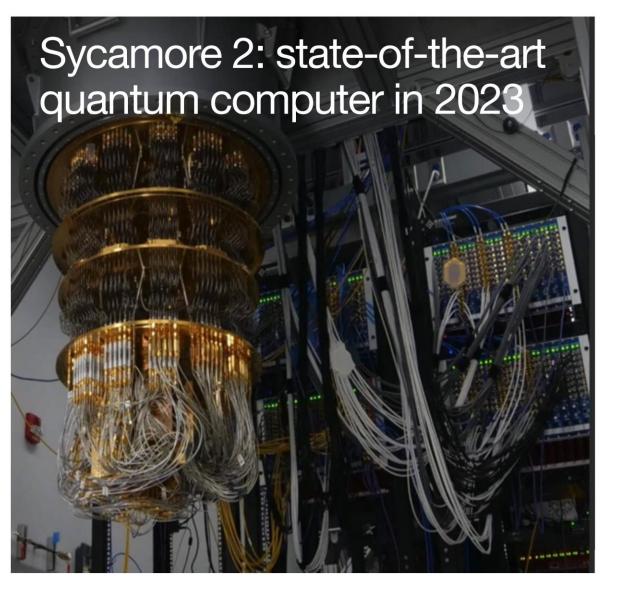

## Sycamore 2: state-of-the-art quantum computer in 2023

#### State-of-the-art Single Flux Quantum (SFQ) chip

#### SEEQC – quantum computer on a chip

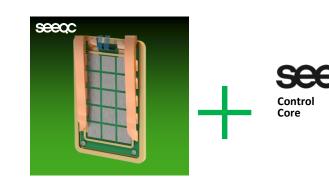

#### Multi-Chip Module (MCM)

Qubit layer – compatible with all leading qubit technologies

Fully integrated quantum computing architecture

- >8-16x Higher multiplexing, removes overhead

- Built-in error correction

- 1,000x Lower energy and heat dissipation

- >10x Faster clock speeds + lower latency

- 128x Lower control pulse complexity

- Superconducting manufacturing commercial-ready

- 400x Cheaper system components

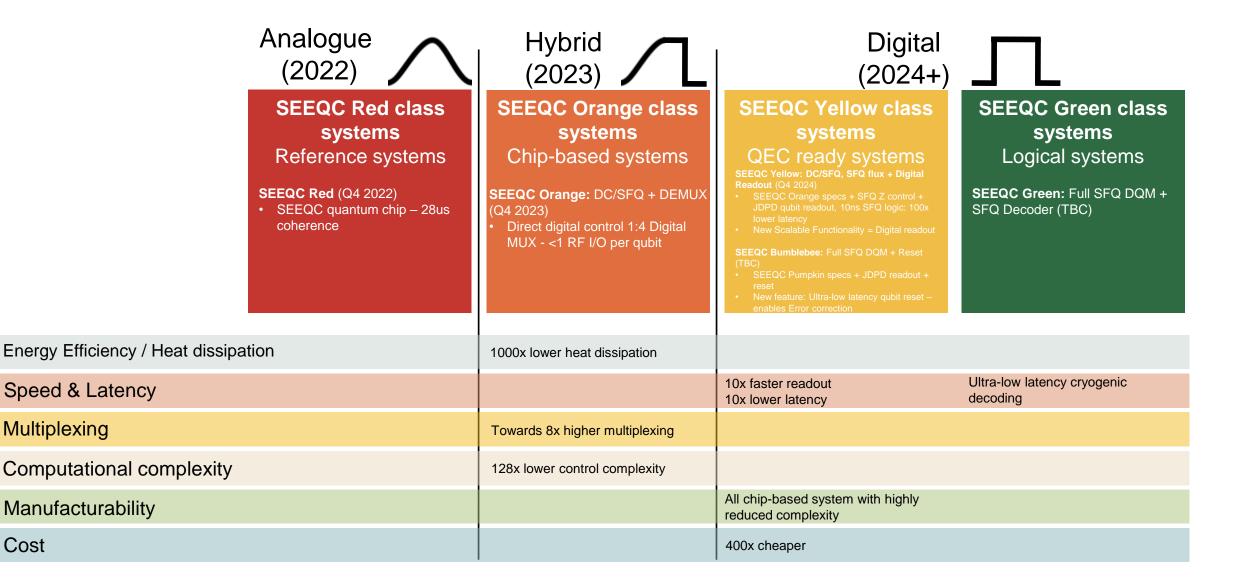

#### SEEQC quantum computing systems roadmap

Cost

#### SEEQC Red: first quantum computer in Italy

CTICUE 2/11/1406/18 SCIENZA 28.84.2023

Abbiamo visto (e provato) il primo computer quantistico in Italia

> COBRIERE DELLA SERA Innovazione

L'INDUSTRIA DEL FUTURO

#### QUANTUM COMPUTER **«PER I CALCOLI ULTRAVELOCI ABBIAMO SCELTO L'ITALIA»**

#### QC + HPC integration: unifying two communities to solve practical problems

### Demand for fast and high-fidelity readout

- 1. A scalable physical system with well characterized qubits

- 2. The ability to initialize the state of the qubits to a simple fiducial state

- 3. Long relevant decoherence time

- 4. A "universal" set of quantum gates

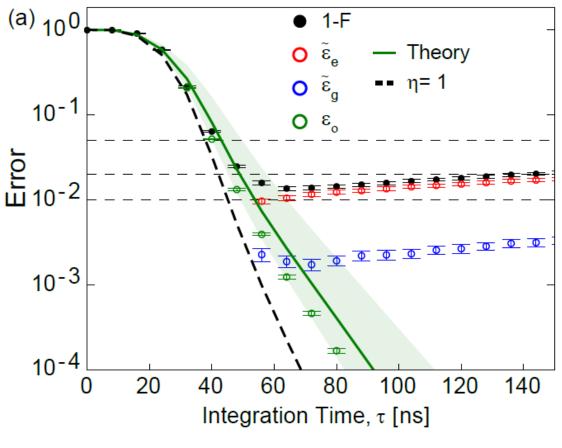

- 5. A qubit-specific **measurement** capability

Error thresholds for fault tolerant QC:  $\epsilon_1 \le 0.1\%$  $\epsilon_2 \le 0.1\%$  $\epsilon_m \le 0.5\%$

D. P. Divincenzo - https://arxiv.org/pdf/quant-ph/0002077.pdf

Martinis, J. M. Qubit metrology for building a fault-tolerant quantum computer. npj Quantum Inform. 1, 15005 (2015).

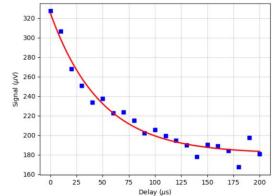

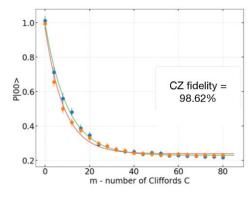

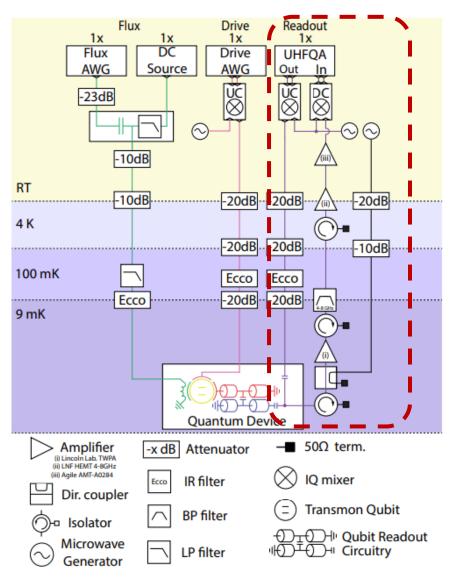

### Demand for fast and high-fidelity readout

T. Walter, at al., arXiv:1701.06933v2 (2017)

J. Heinsoo, et al. arXiv:1801.07904v1 (2018)

F Swiadek, et al., arXiv:2307.07765 (2023)

L. Chen, at al., npj Quantum Information (2023)

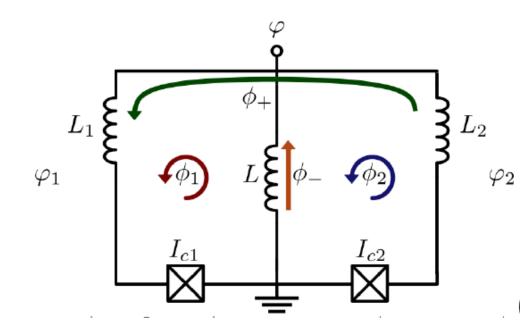

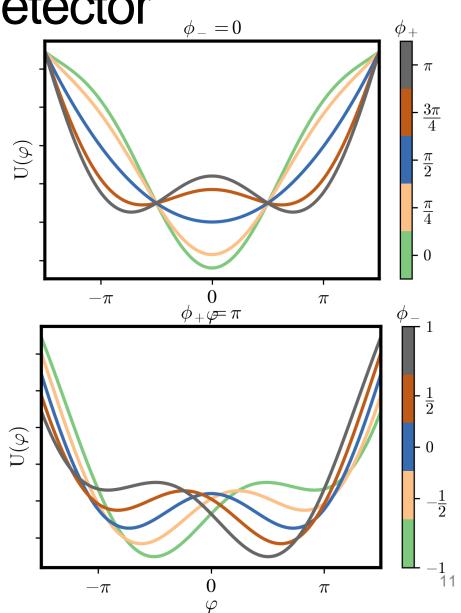

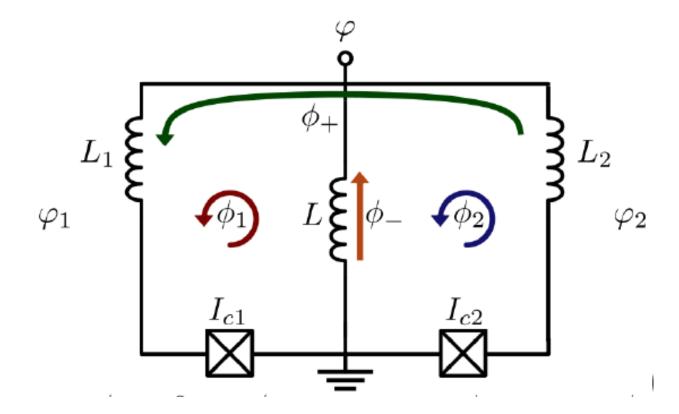

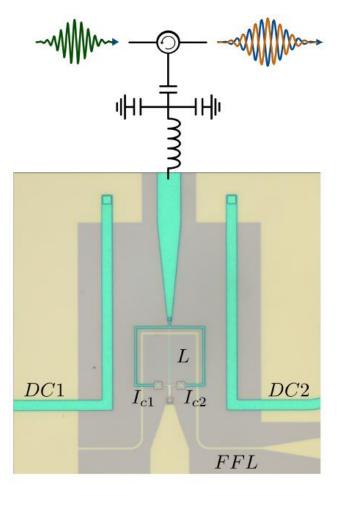

### The Josephson Digital Phase Detector

The potential energy can be written as:

$$U(\varphi) = \frac{1}{2L} \left(\frac{\Phi_0}{2\pi}\right)^2 \varphi^2 - \frac{\Phi_0}{2\pi} 2I_c \cos(\phi_- + \varphi) \cos(\phi_+)$$

### The Josephson Digital Phase Detector

#### Seeqc

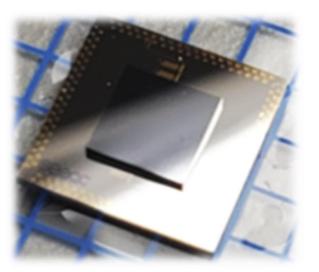

### Fabrication possible at SEEQC commercial foundry

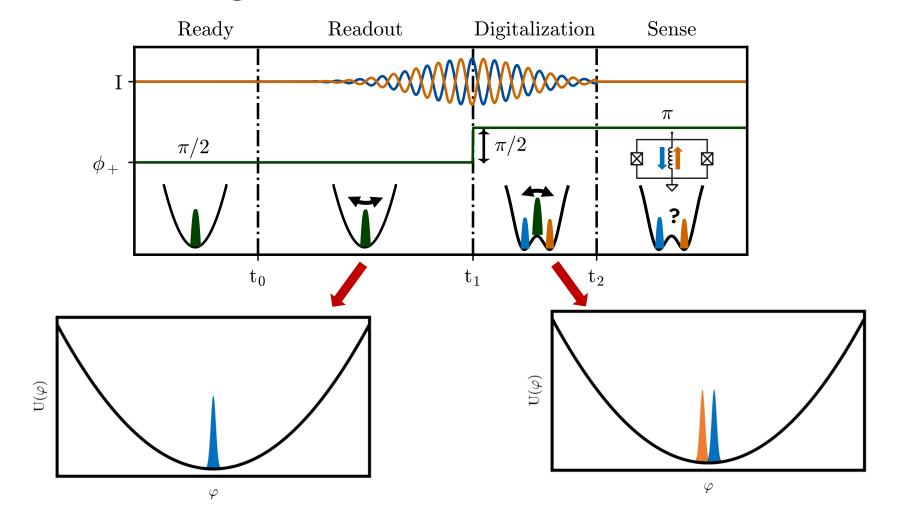

### The Josephson Digital Phase Detector

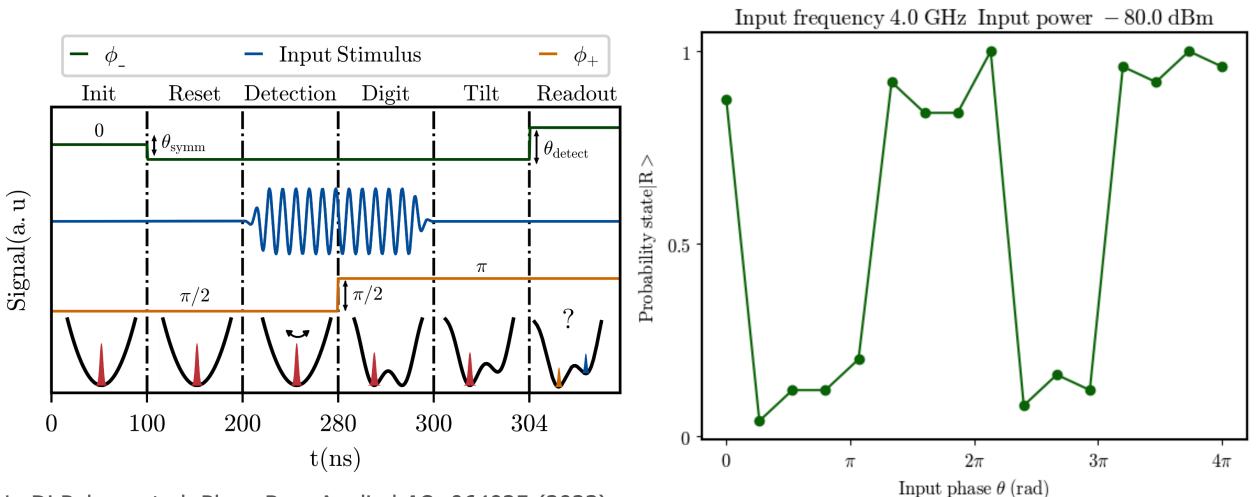

#### The big advantage in scalability comes with SFQ

#### **Quantum-to-Digital Converter:**

- Performs phase detection in time domain using co-located superconducting integrated circuit

- Converts output to digital SFQ data

- Readout multiplexing:

- Digital, e.g., 16:1

- FDM/TDM 8x1

- Self-contained, co-located readout circuit:

- ✓ All readout circuits of part of DQM chip MCM-integrated with qubit chip at 20mK

- All control signals are generated locally in DQM chip: SFQ master clock and trigger, no external signals

Patent pending

### The big advantage in scalability comes with SFQ

|                    | Conventional readout<br>w JPA/TWPA | JDPD w/o<br>SFQ circuitry | JDPD w SFQ<br>circuitry |

|--------------------|------------------------------------|---------------------------|-------------------------|

| Cryo coax lines    | 3                                  | 3                         | 0-1 <sup>c</sup>        |

| AWG channels       | 1-2 <sup>a</sup>                   | 3                         | 0                       |

| CW RF source       | 1-2 <sup>b</sup>                   | 1                         | 0-1°                    |

| Digitizer channels | 2                                  | 2                         | 0                       |

| DC/digital lines   | 0                                  | 0                         | 2-5 <sup>d</sup>        |

a. Depending if IQ-mixing or direct digital synthesis of GHz tones is used.

b. The second is needed if IQ-mixing is used for up/down-conversion of GHz tone.

c. Depending if clock is provided from room temperature or generated on-chip.

d. Depending on SFQ-circuits design.

#### SEEOC

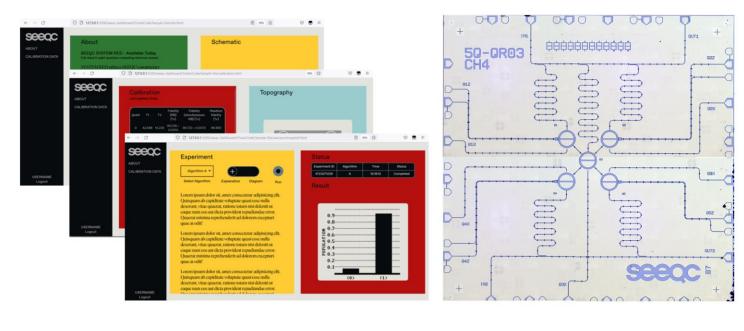

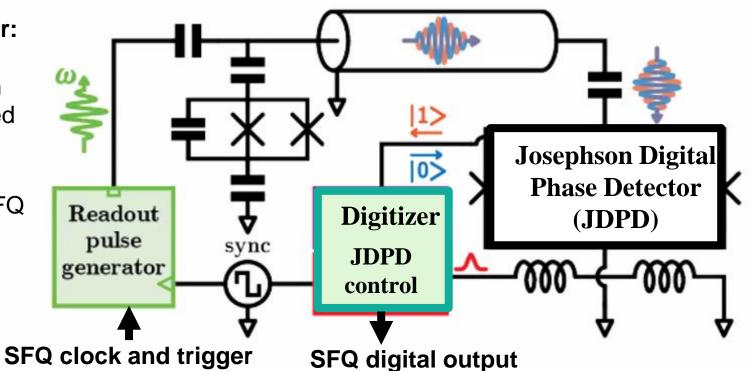

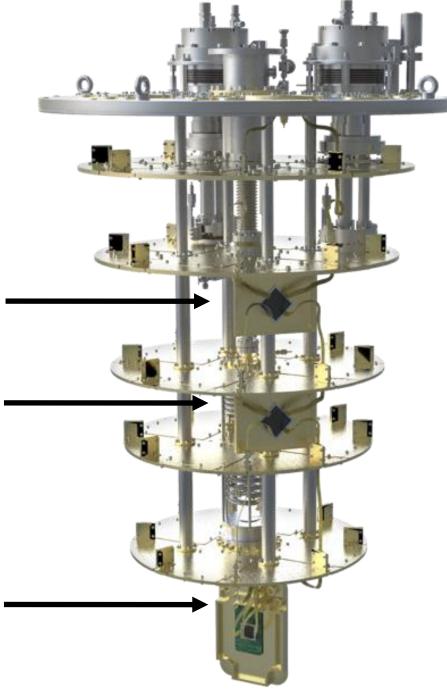

### SFQ-based on chip digital readout

**SEEQC** solution: Multi-layer Processors in Dilution Refrigerator High-speed digital SFQ co-processors + cryoCMOS memory and co-processors High-speed digital SFQ controller + QEC pre-decoder Multi-Chip Module (MCM) Quantum Layer Fit onto a multi-chip module on top of qubits in DR

#### Working towards a data link from QC to HPC

#### SEEQC Announces Digital Chip-Based Collaboration with NVIDIA to Accelerate Quantum Supercomputing

World's first fully digital chip-based quantum-to-GPU integration will enable error-corrected quantum supercomputing

Why it matters...

- The successful integration of SEEQC's chip architecture with NVIDIA GPUs will:

- Create a chip-based quantum-to-GPU computing solution, compatible with all quantum computing technologies (superconducting, silicon spin, photonics, trapped ion, neutral and cold atom, topological).

- Combine the best of classical and quantum computing into Quantum Supercomputing.

- Bring quantum computing closer to datacenter-scale with infrastructure for quantum AI.

- Create the possibility for on-chip, real-time quantum error correction that is necessary for q computers to scale.

SEEQC Orange/Yellow/Green systems + SEEQC Control core platform

Quantum enhanced data center

SEEQC Single Flux Quantum (SFQ) microprocessor chip

# Thank you